Emerging Standards

Colin Pearce

Vendors are employing larger and faster sensors to develop camera systems that address high-speed area-scan and linescan applications. Since high-speed image data must often be transferred over large distances, new interface standards such as CoaXPress are being developed to meet these demands (Fig. 1).

While other high-speed standards remain to be finalized, the CoaXPress specification, anticipated to become an international standard, can trade speeds up to 6.25 Gbits/s with distances up to 40 m (or 130 m at 3.125 Gbits/s) over a single 75-Ω coaxial cable. CoaXPress also specifies an uplink within the same cable carrying 20-Mbit/s control data and 13-W 24 VDC power available to the imaging device supplied from the host. Scalability is also a key strength, as bit rates can start from 1.25 Gbits/s while multiple cables can be used to allow speeds of 25 Gbits/s and beyond.

CoaXPress owes its performance to factors ranging from physical implementation to protocol standards. Low-cost coaxial cable performs well at higher frequencies. Its single core eliminates the signal skew problems that can afflict multicore twisted-pair cables and is less affected by mechanical flexing or electromagnetic interference (EMI) problems. In current CoaXPress implementations, the cable’s high-frequency performance over long distances is realized by termination to EqcoLogic single-chip transceivers at the host computer and camera device end (Fig. 2). Until alternative single-chip transceivers are available, the EqcoLogic chip designs are being held in escrow to futureproof the interests of CoaXPress adopters.

Hardware implementation

The EqcoLogic chipset comprises a high-speed coax line driver with a built-in low-speed receiver for the imaging device and a high-speed receiver with built-in low-speed driver for the host. The receiver also incorporates an auto-adaptive equalizer. This is essential because as cable distance increases and frequencies increase into the gigahertz region, the received signal is increasingly attenuated. While the exact attenuation characteristic depends on the cable type, quality, and length and the signal frequency, the equalizer automatically adapts to produce a complementary gain characteristic in real time, providing a flat output level over the CoaXPress operating frequency range.

The EqcoLogic transceivers facilitate the CoaXPress full-duplex operation by using high-pass filters to separate the gigahertz-level downlink from the 20-Mbit/s uplink. Using 8B/10B coded data, CoaXPress maps 8-bit characters in the packets to be sent over the link into 10-bit characters—an operation that ensures a long-term, even balance of 1s and 0s in the digital data stream. This eliminates DC bias, allowing high-pass filtering without loss of data. Clock recovery from the received data is also improved. It also readies the protocol for fiber-optic solutions in the future.

The 8B/10B scheme specifies K-codes—control characters—as well as data characters. These are used for formatting and indication purposes such as “start of data packet.” At the transport layer, CoaXPress transmissions are organized as words, which generally comprise four characters. Before transmission, these are assembled into packets, bounded by Stream Packet Header (SPH) and Stream Packet Trailer (SPT) characters. The protocol allows transmission of both rectangular and nonrectangular images. Multiple data streams can also be handled.

The data stream includes two methods of error detection and management. First, 32-bit CRC checks are applied to all data sent over CoaXPress that are decoded by the receiver. Second, the control protocol is immune to single-bit transmission errors by sending key data multiple times and voting out any erroneous characters.

CoaXPress also allows for in situ testing of the complete imaging chain from the device through the cable to the host. Testing involves transmitting a known data sequence to allow measurement of the bit-error rate (BER) by the host. This can be used as a self-test during startup as well as a diagnostics tool to identify unreliable cables or connections.

Latency and jitter

The CoaXPress protocol also allows trigger events to be sent from host to camera and vice versa with minimal latency and jitter. At the VISION tradeshow in Stuttgart (Nov. 9–11, 2010), the Japan Industrial Imaging Association (JIIA) demonstrated how a test setup consisting of a CoaXPress frame grabber interfaced to a CoaXPress camera could be used to measure this latency.

By using test points hooked to both the camera and the frame grabber, JIIA showed how the CoaXPress timing specification was used to accurately recreate trigger signals sent from the frame grabber to the camera. A video demonstration of this by Chris Beynon of Active Silicon can be viewed at http://bit.ly/faEGpp. As can be seen, the measured fixed latency of the trigger signal was 3.66 µs.

In a similar way to latency, the jitter may be calculated and measured. Jitter is the variation in time of a presented event from a nominally ideal position. Typically the jitter is due to a clock running asynchronously to a desired periodic trigger position. In the same demonstration, the trigger jitter measured between 10 and 11 ns with an internal 125-MHz clock. Since CoaXPress specifies a maximum trigger sampling clock rate of 250 MHz, this jitter can be reduced to around 5 ns.

Using a CoaXPress device is a plug-and-play operation. Upon power-up, the protocol discovers the presence of a connected device automatically sets up the link in terms of bit rate and link configuration scheme. CoaXPress can also manage the device and host setup parameters such as image format, bit depth, and data packing format. Where convenience of configuration is a priority, the standard also supports the GenAPI, GenTL, and SFNC (Standard Features Naming Convention) module of the GenICam v2.0 standard or higher.

FPGA implementation

The CoaXPress protocol functionality is typically handled by field-programmable gate arrays (FPGAs) in both the camera and the host. The FPGA’s high-speed serializer/deserializer functionality interfaces directly with the physical interface layer, implemented by EqcoLogic transceivers. In the camera, the FPGA formats, packetizes, and adds CRC bits to each video data stream, and combines these with control and trigger packets.

The FPGA then prioritizes the packets and manages link sharing before outputting the packets to the serializer/deserializer. It also decodes and depacketizes the 8B/10B control and trigger data received from the low-speed uplink. The FPGA implementation in a frame grabber host provides the reverse functionality at the other end of the link as well as managing the power supply startup for the Power over CoaXPress (PoCXP) requirements of the specification.

In addition to single 75-Ω cable types designated as CXP-3 (3.125 Gbits/s) and CXP-6 (6.25 Gbits/s), there are multicable types known as Dual CXP-6 (12.5 Gbits/s) and Quad CXP-6 (25 Gbits/s). In fact, a number of cables can be added to provide n × 6.25 Gbits/s performance over a 40-m cable. Choices can also be made in the quality and type of cables and connectors used. Larger-diameter cables can be employed for longer distances, and thinner, more flexible, lower-cost cables for shorter runs. Also, during upgrades, existing 75-Ω cable installations can often be used for shorter distances and/or lower speeds.

First products

First products—cameras, frame grabbers, converters, and cable solutions—are in development by many companies, some of which were recently demonstrated at the VISION 2010 show. These included the world’s first CoaXPress linescan camera, the XCM8040SA—an 8k × 1-pixel, 8-bit/pixel camera from Nippon Electro-Sensory Devices Corp. (NED) running at 2.5 Gbits/s, which was shown transmitting data to an Active Silicon frame grabber over the interface at a distance of 100 m (Fig. 3). These products are to be based on the v1.0 specification that is available from the JIIA.

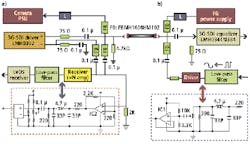

As part of the standards ratification process, the JIIA has also developed an equivalent circuit for the CoaXPress specification that uses off-the-shelf devices from National Semiconductor. In this way, camera and frame grabber designers have the flexibility of multisourced chip solutions for the physical interface. This circuit, which was demonstrated as a prototype at VISION 2010, uses National Semiconductor’s LHMH0302 3G-SDI driver in the camera to implement the high-speed 3.125-Gbit/s downlink. A 3G-SDI equalizer on the frame grabber side then performs signal equalization (Fig. 4). Analog circuits on the transmitter (frame grabber) side provide the low-speed uplink signal. This is then filtered on the receiver (camera) side and converted to a low-voltage differential signal (LVDS).

Following the worldwide launch of CoaXPress v1.0 in Japan, Europe, and North America, volume production deliveries are expected to start in 2011.

Further developments in the CoaXPress specification are likely to include micro-coax; miniature and multiway connectors; a dedicated high-speed uplink (using multicore coax) for high-speed triggering applications; options for using optical fiber; and methods to transport metadata. Further information is available at www.coaxpress.com.

Colin Pearce is chief executive officer at Active Silicon Ltd. (Iver, UK; www.activesilicon.com).

Company Info

Active Silicon Iver, UK www.activesilicon.com

Altera San Jose, CA, USA www.altera.com

EqcoLogic Brussels, Belgium www.ecqologic.com

Japan Industrial Imaging Association (JIIA) Tokyo, Japan www.jiia.org

National Semiconductor Santa Clara, CA, USA www.national.com

Nippon Electro-Sensory Devices Corp (NED) Osaka, Japan www.ned-sensor.co.jp

XilinxSan Jose, CA, USA www.xilinx.com