Camera Link HS: The Path to 50 Gbps and Beyond

Bob McCurrach, Mike Miethig, and Martin Schwarzbauer

Driven by demand for higher-precision imaging in a broad range of applications, sensor and camera manufacturers are pushing the limits of resolution with smaller pixel sizes, increasingly higher pixel counts, and higher frame rates. This progress comes with interface protocol advances to transmit larger amounts of image data at increased speeds.

Several standardized protocols are available, and Camera Link HS is one of the leaders in speed, reliability, ease of development, and bandwidth. Camera Link HS is poised to provide significantly expanded capability in upcoming releases, with changes that promise to make it the standout choice for camera interfacing.

From Camera Link to Camera Link High Speed

Camera Link High Speed (Camera Link HS or CLHS) is a mature and robust interface standard for industrial cameras and systems. It evolved from Camera Link, the vision industry’s first standard camera interface protocol. Originally released in 2000, Camera Link was a completely volunteer-developed protocol hosted by the Association for Advancing Automation (A3) featuring real-time, high-bandwidth, parallel two-way communications between the camera and frame grabber. In addition to real-time high-speed transfer at very low latency, Camera Link provided standardized connectivity with low cable costs as well as power over the interface connection (PoCL).

CLHS was introduced in 2012 and built on the low-latency, zero-jitter, real-time strengths of Camera Link. The CLHS standard further provided scalable bandwidths with extremely reliable data delivery, support for both copper and fiber cabling, and, importantly, Intellectual Property (IP) cores for ease of component development.

A3 hosts a number of technical committees that develop and maintain digital interface standards and interface code, one of which is CLHS. Currently at version 1.1, CLHS implements its protocol with two physical layer encodings: M Protocol and X Protocol. The VHSIC Hardware Description Language (VHDL) IP cores available from A3 have been implemented in Altera, Xilinx, and Microsemi FPGAs. Used in components such as cameras and frame grabbers, the cores are available from A3 at a price point of $1,000 to help promote the standard and speed proliferation of the technology.

The inexpensive IP core infrastructure helps camera and frame grabber manufacturers speed CLHS development and implementation. Because CLHS IP core code is open-source, licensed users can customize the core for their own use. They can improve it by adding features that, upon technical review and approval, can become a permanent part of the IP core.

The CLHS M Protocol IP core features well-proven and mature 8b/10b line encoding for use in lower-cost and lower-power FPGAs. It supports hardware with copper (C2) cabling, with CX4 connections up to 15 meters and 2.1 Gbps in the CLHS cable. Active plug-on fiber cable can be added externally to achieve up to 100 meters. Typical bit rates for the M Protocol are up to 5 Gbps per lane.

The CLHS X Protocol IP core is designed for 10-Gbps and higher bit rates using 64b/66b line encoding. Other interface protocols, such as CoaXPress (CXP), are moving to this encoding structure. Note that because of the line encoding technique, CLHS 10 Gbps is equivalent to CXP 12.5 Gbps. The X Protocol also has forward error correction and single-bit error immunity. This protocol is designed to natively support fiber connections F2 (SFP+) and soon to be introduced F3—quad small-form-factor pluggable (QSFP+) and multifiber push-on (MPO)—connectors at rates up to 16 Gbps per lane. Copper CX4 (C3) connections still are supported, but the highest data rates and cable lengths (as much as 20 kilometers or more, in some cases) are realized using fiber cabling. Importantly, the 64b/66b encoded X Protocol has been in production since 2012 and has a long history of field-tested stability.

Five message types are available in CLHS: a low-latency (<1-µs) 0-ns jitter trigger for real-time imaging at up to 8 MHz with seven separate modes, 16 bidirectional general-purpose I/Os with <1-µs latency, remote DMA video packet and frame grabber data forwarding, high-speed command uplink enabling streaming correction coefficients, and revision information used in device discovery. One of the big values of CLHS is that it is a real-time, point-to-point interface. In the context of the CLHS triggers and GPIO, the low latency means immediate responses, eliminating the need for tracking and scheduling as might be the case with other interfaces.

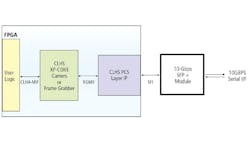

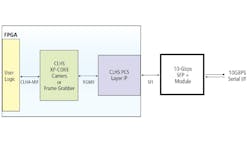

The CLHS X Protocol can connect to an 10GBASE-KR Ethernet PHY physical; Figure 1) for FPGAs that don’t have built in 10-Gbps transceivers or use the provided Physical Coding Sublayer (PCS) module to implement the code within 10-Gbps-capable FPGAs that don’t offer the 10GBASE-KR capability (Figure 2). Because of the unique way the CLHS X Protocol is implemented, Camera Link HS is already in the final stages of moving the specification to 25 Gbps.

Ready for 25 Gbps

The well-designed IP core architecture makes CLHS ready without any modification to move to 25 Gbps on an FPGA using 25-Gbps transceivers over fiber with SFP28 or QSFP28 or MPO connectors. The soon-to-be-released specification revision will validate CLHS as having up to 100-Gbps (4 × 25Gbps) available bandwidth using a single MPO connector.

In achieving this speed increase, the CLHS X Protocol IP core remains completely unchanged. Therefore, all existing CLHS infrastructure also remains unchanged, making the move to 25 Gbps inexpensive and straightforward for vendors and users. Contrast this with frame grabber interfaces that need to change core code and move to different line encoding to implement faster rates. Furthermore, CLHS has a very flexible and robust mechanism for changing the speed of the interface. Using MPO to LC, breakout cables, or SFP28 allows backward compatibility to existing CLHS 10-Gbps frame grabbers or newly developed 25 Gbps frame grabbers to support existing 10G cameras.

Getting to 50 Gbps and Beyond

With FPGA and PHY technology ready to support 50-Gbps and higher rates, Camera Link HS is poised to deliver powerful real-time camera interfacing at even higher imaging rates. The features and capabilities already in place in the CLHS standard stand to make the path to 50 Gbps effortless. The CLHS working group has leveraged the existing X Protocol IP core, adding a simple bridge from the 64-bit output of the X Protocol IP core PCS to the 128-bit input of 50-Gbps FPGAs with built-in SerDes blocks.

To achieve 50-Gbps speeds, CLHS will introduce a virtual channel using a master and slave channel (or lane) all in one fiber. With this minor change in the specification, component vendors will be able to easily migrate to the higher-speed interfacing with minimal impact on hardware and software architecture.

Future of Frame Grabbers

The Camera Link HS standard is built for the future of imaging in its implementation of general IP cores, open-source VHDL, and inherent advanced line encoding and error correction. One key to future-proofing the standard is the seamless support for fiber cabling, something that may become standard in most imaging environments. Fiber cable is not fragile or more susceptible to bending, wrapping, or pinching than traditional copper wire. With current technologies, fiber is easy to work with and is field installable and modifiable. Able to carry more than twice the bandwidth of copper at distances of many kilometers, fiber is also less expensive than copper wire.

Already a robust imaging interface, Camera Link HS continues to improve. Its use of 64b/66b encoding in 2012 still provides manufacturers and end users a long design cycle from 10 Gbps all the way up to 50 Gbps. The standard’s many features and capabilities make it stand out as a definitive choice in high-speed imaging applications both now and in the future

Bob McCurrach is Director of Standards Development, A3 (Ann Arbor, MI, USA). Mike Miethig is Technical Manager, Teledyne DALSA (Waterloo, ON, Canada). Martin Schwarzbauer is Manager Camera Systems (Product Development), Excelitas PCO GmbH (Kelheim, Germany).