FPGAs speed satellite data classification

FPGAs speed satellite data classification

Marco A. Figueiredo

Giga Operations (Berkeley, CA) has collaborated with NASA`s Microelectronics Systems Branch in prototyping a system for processing satellite information. To prove the concept, NASA selected a multispectral image-classification algorithm based on a probabilistic neural network (PNN) that classifies different types of land.

The PNN algorithm takes each pixel in an image and compares it against sets of pixels, called weights, known to belong to certain landmass classes. The PNN calculation derives a value for each class indicating the probability that the input pixel fits in one particular class. The highest value derived from the PNN calculation indicates the best possible class for the original pixel.

The fine-grain-parallelism characteristics of the PNN classification algorithm allow it to be mapped to an FPGA coprocessor. Each type of PNN calculation is treated as a processing element (PE) that is mapped to an FPGA module. Parallel computation is achieved by configuring other coprocessor modules with a PE and presenting each module with a different pixel to be classified.

The PNN requires 26,000 floating-point operations to classify a pixel among five classes with 400 weights per class. In a benchmark experiment, a 200-MHz Digital Equipment Corp. Alpha took 12 minutes to classify a 512 ¥ 512, four-band LANDSAT2 image. On a 166-MHz Pentium equipped with two FPGA coprocessor modules, the same task took 1.5 minutes. The results are so promising that NASA may replace hundreds of minicomputers with PCs equipped with parallel reprogrammable engines.

NASA Goddard Space Flight Center

Greenbelt, MD

E-mail: [email protected]

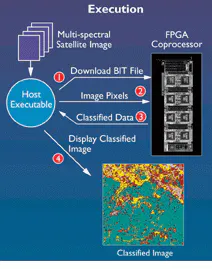

NASA`s satellite data processor is controlled by a host executable program that determines what type of processing needs to take place. Xilinx programming configuration files (BITfiles) are then sent to a GigaOps programmable gate array where board image data are processed. Data are then returned to the host for display.